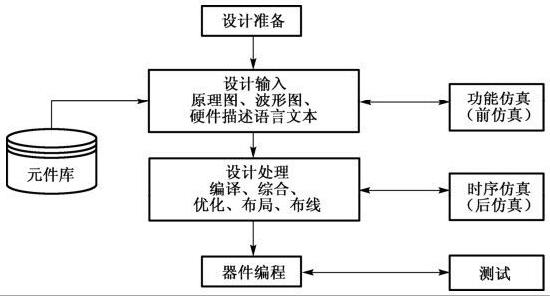

平板定制方案基于EDA软件的开发流程如图1所示,这个开发流程对于CPLD、FPGA器件的设计具有一般性的指导意义。下面,将分别介绍该流程图中各个操作步骤的功能特点。

图1 基于EDA软件的开发流程

1.平板定制方案设计准备

在进行项目设计之前,首先要进行方案论证、系统设计和器件选择等准备工作。现在多采用自上而下的设计方法,也可以采用传统的自下而上的设计方法。

2.平板定制方案设计输入

将开发人员设计的电路系统以一定的表达方式输入计算机,这是进行FPGA/CPLD开发的最初步骤。通常,使用EDA工具的设计输入可分为两种类型。

(1)图形输入。图形输入通常包括波形图输入、状态图输入和原理图输入等,其中波形图输入是将待设计的电路看成一个黑盒子,只需告诉 EDA 该黑盒子中电路的输入和输出时序的波形图,EDA即可据此完成黑盒子电路的设计。

状态图输入是根据电路的控制条件和不同的转换方式,用绘图的方法在 EDA 的状态图编辑器上绘出状态图,然后由 EDA 编译器和综合器将此状态变化流程图形编译综合成电路网络表文件。

原理图输入是一种类似于传统电子设计方法的编辑输入方式,即在 EDA 的图形编辑界面上绘制能完成特定功能的电路原理图。原理图由逻辑器件(符号)和连接线构成,这些元件通常存储在元件库中,设计时需要什么元件就从元件库中直接调用该元件的符号。原理图输入的优点是直观,便于观察信号和调整电路;其缺点是设计修改不方便,从元件库中调图比较繁杂。

(2)硬件描述语言文本输入。这种方式与传统的计算机软件语言编辑输入基本一致,就是用文本方式描述设计,编辑输入某种硬件描述语言的电路设计文本(如 VHDL 或 Verilog的源程序)。硬件描述语言文本输入的优点是:语言与工艺无关,可以使开发者在系统设计、逻辑验证阶段便确立方案的可行性;语言的公开可利用性便于实现大规模系统的设计;无须熟悉底层硬件电路和PLD。

3.平板定制方案功能仿真

仿真就是让计算机根据一定的算法和仿真库中的资源对 EDA 设计进行模拟,以验证设计,排除错误。功能仿真也称为前仿真,是最基本的仿真验证,它基于设计布线和配置之前的网络表文件,直接对VHDL、原理图或其他形式描述的逻辑电路进行测试模拟,以了解其实现的功能是否满足原设计要求的过程,不涉及任何具体器件的硬件特性,不经历适配阶段。在设计项目编译后即可进入门级仿真器进行模拟测试。

常用的功能仿真工具有Mentor Graphics公司的ModelSim和QuestaSim、Synopsys公司的VCS(Verilog Compiled Simulator),以及Cadence公司的NC-Verilog Simulator等,下面以ModelSim为例介绍仿真器的基本功能。

ModelSim是工业界通常应用的仿真器之一,也是唯一的一种单核、支持多语言混合仿真的仿真引擎,其支持Verilog、VHDL、SystemVerilog、System C、C、C++(可选)等语言,具有Verilog、VHDL及System C语言的全调试能力,内部集成了C/C++、PLI(Programming Language Interface)/FLI(Foreign Language Interface)和System C的集成C调试器,支持众多ASIC和FPGA厂家库,可以用于FPGA、ASIC设计的RTL和门一级电路的仿真。

通过功能仿真,用户可以验证整个系统的逻辑功能是否正确,可以通过查看仿真波形来对系统的逻辑功能进行分析,并可以以此为依据,对设计进行必要的修改和完善。

4.平板定制方案设计处理

设计处理是可编程逻辑器件设计的核心环节,在设计处理过程中,编译软件将对设计输入进行逻辑化简、综合优化和适配,最后产生编程文件。

(1)语法检查和设计规则检查。设计输入完成后,首先进行语法检查,列出错误报告供设计人员修改;然后进行设计规则检查,检查总体设计是否超出器件资源或规定的限制,并通过报告列出,指明违反规则的情况以便设计人员纠正。

(2)逻辑优化和逻辑综合。逻辑优化的目的是化简所有的逻辑方程或用户自建的宏,使设计所占用的资源最少。平板定制方案逻辑综合的目的是将多个模块化文件合并成门一级或者更底层的网络表文件,并使层次设计平面化,这项工作由综合器完成。综合器的功能就是将硬件描述语言的描述与给定的硬件结构用某种网络表文件的方式对应起来,形成相应的映射关系,在综合器工作前必须给定目标硬件结构参数。如果把综合理解为映射过程,那么显然这种映射不是唯一的,并且综合的优化也不是单纯的或一个方向的。为达到速度、面积、性能的要求,往往需要对综合加以约束,这称为综合约束。

(3)适配和分割。该阶段确立优化以后的逻辑能否与器件中的宏单元和I/O单元适配,平板定制方案然后将设计分割为多个便于识别的逻辑小块,并映射到器件相应的宏单元中。如果整个设计较大,不能装入一片器件时,可以将整个设计分割划分(分割)成多块,并装入同一系列的多片器件中。分割可以完全自动完成,也可以部分或全部由用户控制完成,其目的是使器件数目最少,器件之间的通信引脚数目最少。

(4)布局和布线。布局和布线工作是在上述工作完成后由软件自动完成的,它以最优的方式对逻辑器件布局布线,并准确地实现器件逻辑或者联合设计时器件间的互连。

5.平板定制方案时序仿真

时序仿真也称为后仿真或延时仿真,是接近真实器件运行特性的仿真。由于不同器件内部的延时不一样,不同的布局和布线会给延时造成不同的影响,因此在设计处理后,对系统和各模块进行时序仿真,分析其时序关系,估计设计性能,这对检查和消除竞争冒险是非常有必要的。时序仿真产生的仿真网络表文件中包含了精确的硬件延时信息。

6.平板定制方案器件编程、下载和测试

时序仿真完成后,软件就可以产生供器件编程使用的数据文件。对CPLD来说,就是产生熔丝图文件,即 JED(满足 JEDEC 标准)文件,熔丝图文件内含器件内部互连逻辑。对FPGA 来说,就是产生位流数据文件,然后通过编程器或编程电缆把位流数据文件下载到FPGA器件的外部存储器中,待工作时再调入FPGA中运行。

通常,将对CPLD的下载称为编程(Program),而对FPGA中的SRAM进行直接下载的方式称为配置(Configure),平板定制方案但对于反熔丝结构和Flash结构的FPGA的下载,以及对FPGA的专用配置ROM的下载仍然可以称为编程。

最后,对含有编程数据的FPGA或CPLD硬件系统进行全面的测试,验证设计逻辑在目标系统上的实际工作状况。