三防平板方案设计中混合模块路径延迟和分布式延迟

三防平板方案设计中如果模块包含模块路径延迟和分布式延迟(模块内原语实例的延迟),将选择每个路径内两个延迟中较大的一个。混合模块路径延迟和分布式延迟例子1。

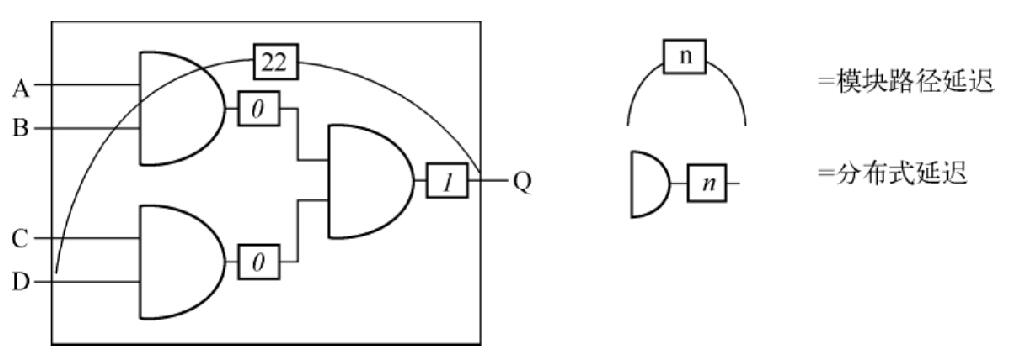

图1 给出了利用分布式延迟和路径延迟组合建模的简单电路(仅示出了D输入到Q输出路径)。这里,从输入D到输出Q的模块路径上的延迟是22,而分布式延迟的总和是0+1=1。因此,由D上的跳变引起的Q上的跳变将在D上的跳变后22个时间单位发生。

图1 模块延迟比分布式延迟要长混合模块路径延迟和分布式延迟例子2。

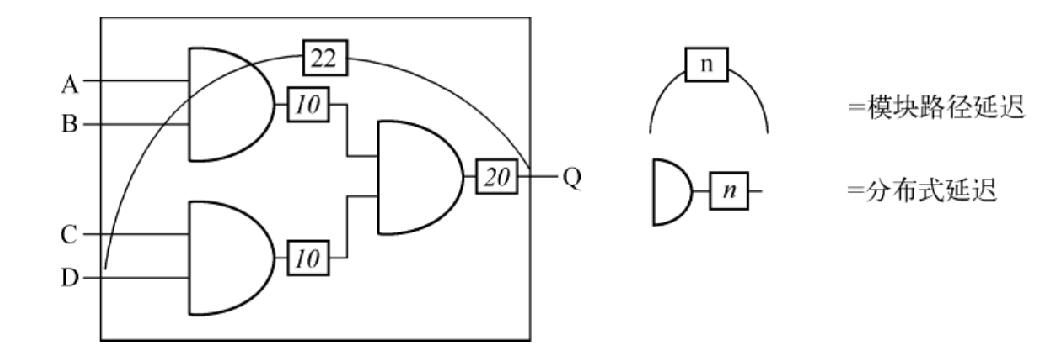

在图2中,从D到Q的模块路径上的延迟为22,但沿着该模块路径的分布式延迟现在加起来为10+20=30。因此,由D上的事件引起的Q上的事件将在D上事件发生30个时间单位后发生。

图2 模块延迟比分布式延迟要短

2、三防平板方案设计中驱动布逻辑

在模块内,模块路径的输出网络不超过一个驱动器。因此,在模块路径输出时,不允许线逻辑。

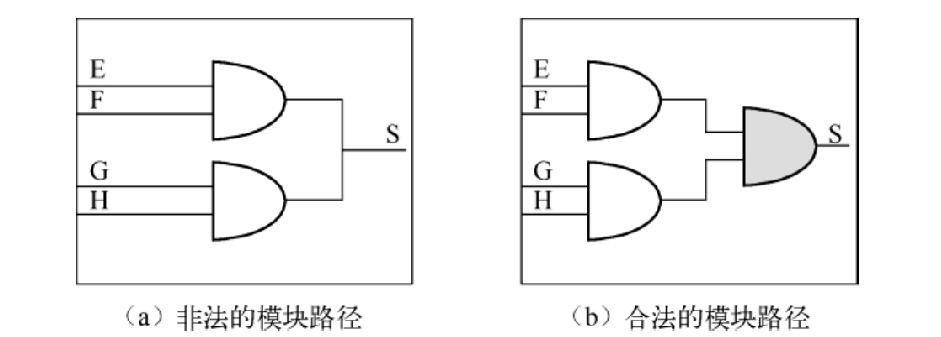

图3给出了出现布线输出规则的冲突,以及避免规则冲突的一个方法。如图1.5(a)所示,由于一个路径由两个逻辑门的输出驱动器,因此所有连接到网络S的模块路径都是非法的。如图1.5(b)所示,假设信号S 是“线与”的,通过放置包含门逻辑的布线逻辑来创建连到输出的一个驱动器,就能规避这个限制。

图3 非法和合法模块路径

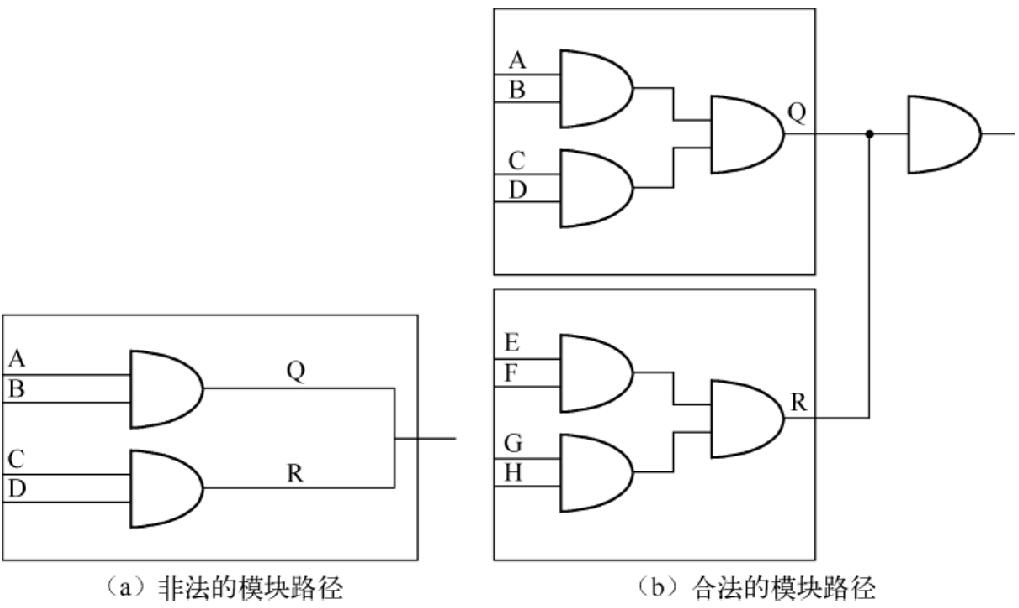

图4(a)的模块路径描述是非法的,当把Q和R连接到一起时,则产生规则冲突条件。尽管在相同的模块内禁止多个输出驱动器连接到一个路径目的端,但是在模块外是允许的。图1.6(b)给出的模块路径描述是合法的。

图4 非法和合法模块路径

3、 三防平板方案设计中脉冲过滤行为的详细控制

在时间上,将比模块路径延迟更接近的两个连续调度的跳变看作脉冲。默认,拒绝模块路径的输出脉冲。连续的跳变不能比模块输出延迟还要靠近,称为脉冲传播的惯性延迟模型。

脉冲宽度范围控制如何处理模块路径输出的脉冲,包括:

(1)应拒绝脉冲宽度的范围;

(2)允许脉冲传播到路径目的的脉冲宽度范围;

(3)脉冲应在路径目的处生成逻辑x的脉冲宽度范围。

三防平板方案设计中两个脉冲限制值定义了与每个模块路径跳变延迟相关的脉冲宽度范围,这两个脉冲限制值为错误限制值和拒绝限制值。错误限制值应该至少和拒绝限制值一样大。不会过滤掉大于或等于错误限制值的脉冲(通过)。小于错误限制值但大于或等于拒绝限制值的脉冲过滤为x。拒绝小于拒绝限制值的脉冲。默认,将错误限制值和拒绝限制值设置成与延迟相等。这些默认值产生完整的惯性脉冲行为,拒绝所有小于延迟的脉冲。

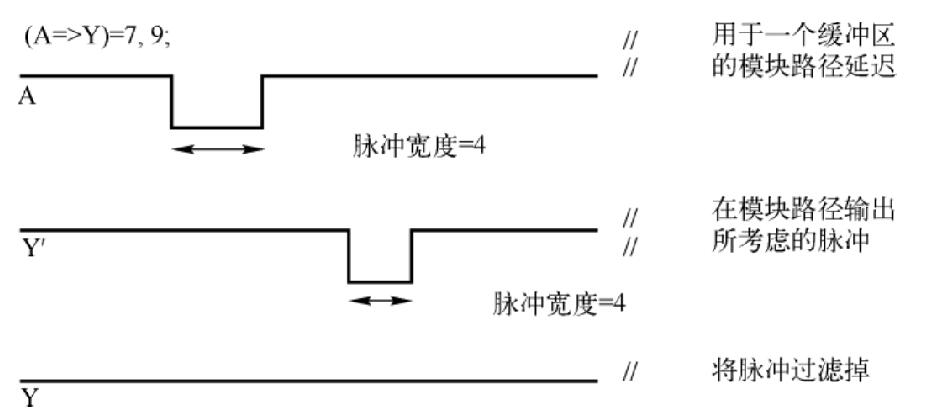

如图5所示,从输入A到输出Y的上升延迟为7、下降延迟为9。默认情况下,上升延迟的错误限制值和拒绝限制值都是7。下降延迟的

错误限制值和拒绝限制值都是9。与形成脉冲的后沿延迟相关联的脉冲极限确定是否以及如何对脉冲进行滤波。波形Y’显示了无脉冲过滤产生的波形。脉冲宽度为2,小于上升延迟7的拒绝限制值;因此如波形Y所示对脉冲进行滤波。

图5 由于脉冲宽度小于模块路径延迟,因此过滤掉脉冲

三防平板方案设计中有三种方法可以从默认值修改脉冲限制值。首先,Verilog语言提供PATHPULSE$ specparam来修改默认值的脉冲限制值。其次,调用选项可以指定应用于所有模块路径延迟的百分比,以形成相应的错误限制值和拒绝限制值。第三,SDF注解可以单独注解每个模块路径跳变延迟的错误极限和拒绝极限。1.指定块控制脉冲限制值

可以使用PATHPULSE$ specparam从指定块内设置脉冲极限值。使用PATHPULSE$指定拒绝限制值和错误限制值的语法格式为

其中,reject_limit_value为拒绝限制值;error_limit_value为错误限制值;specify_input_terminal _descriptor为输入终端描述符;specify_output_terminal_descriptor为输出终端描述符。

如果只指定了拒绝限制值,则应同时适用于拒绝限制值和错误限制值。

可以针对特定模块路径指定拒绝限制值和错误限制值。当没有指定模块路径时,拒绝限制值和错误限制值应适用于模块中定义的所有模块路径。如果路径特定的PATHPULSE$指定参数和非路径特定的PATHPULSE$指定参数出现在同一模块中,则路径特定的参数应优先于指定的路径。

模块路径输入终端和输出终端应符合模块路径输入和输出的规则,但有以下限制,即终端不能是向量的位选择或部分选择。

三防平板方案设计中当模块路径声明声明多个路径时,PATHPULSE$ 指定参数应仅指定给第一个路径输入终端和第一个路径输出终端。三防平板方案设计中指定的拒绝限制值和错误限制值应适用于多路径声明中的所有其他路径。应忽略指定除第一路径输入和路径输出终端以外的任何内容的PATHPULSE$指定参数。【例1.31】PATHPULSE$修改脉冲限制值Verilog HDL描述的例子,如代码清单1-19所示。代码清单1-19 PATHPULSE$修改脉冲限制值的Verilog HDL描述

在该例子中,三防平板方案设计中通过第一个PATHPULSE$,路径clk=>q获取的拒绝限制值为2、错误限制值为9,如第一个PATHPULSE$声明所定义。路径(clk*>q)和(pre*>q)接收第二个PATHPULSE$声明的拒绝限制值0和错误限制值4。路径data=>q没有使用PATHPULSE$明确的说明,因此它获得的拒绝限制值和错误限制值为3,正如第三个PATHPULSE$声明所定义的那样。2.全局控制脉冲限制值

两个调用选项可以指定全局应用于所有模块路径跳变延迟的百分比。错误限制调用选项指定用于其错误限制值的每个模块路径跳变延迟的百分比。拒绝限制调用选项指定用于其拒绝限制值的每个模块路径跳变延迟的百分比。百分比值为0~100之间的整数。

拒绝和错误限制调用选项的默认值都是100%。当两个选项都不存在时,则每个模块跳变延迟的100%用作拒绝和误差限制。

如果错误限制百分比小于拒绝限制百分比,则为错误。在这种情况下,错误限制百分比设置为等于拒绝限制百分比。

当同时存在PATHPULSE$和全局脉冲限制调用选项时,应优先考虑PATHPULES$值。3.脉冲限值的SDF注解

三防平板方案设计中SDF注解可用于指定模块路径跳变延迟的脉冲限制值。当存在PATHPULSE$、全局脉冲限制调用选项和脉冲限制值的SDF注解时,SDF注解值优先。4.详细的脉冲控制能力

脉冲过滤行为的默认类型有两个缺点。首先,对x状态的脉冲过滤可能不够“悲观”,x状态的持续时间太短而不起作用。第二,不相等的延迟可以导致脉冲拒绝,只要后沿在前沿之前,就不会留下脉冲被拒绝的指示。