三防平板方案随着电子系统数字化进程的发展,以及实用性要求的不断提高,可编程逻辑器件得到了越来越广泛的应用,如智能仪表、实时工控、通信设备、航空航天、机器人等领域。

三防平板方案可编程逻辑器件(PLD)可以完全由用户通过软件进行配置和编程,从而完成某种特定的逻辑功能,它是20世纪70年代在专用集成电路ASIC设计的基础上发展起来的新型逻辑器件,到目前为止,可编程逻辑器件已经成为半导体领域中发展最快的产品之一。

随着可编程逻辑器件应用的日益广泛,许多IC制造厂家涉足这个领域。目前在这个领域中,著名供应商的有Altera、Xilinx、Lattice等公司。

1.三防平板方案CPLD和FPGA概述

在 PLD 器件中有重要的两大类:复杂可编程逻辑器件(CPLD)和现场可编程门阵列(FPGA)。两者的功能基本相同,只是实现原理略有不同。

CPLD是从PAL和GAL器件发展出来的器件,相对而言规模大、结构复杂,属于大规模集成电路范围,是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(在系统编程)将代码传送到目标芯片中,实现设计的数字系统。

FPGA 是在 PAL、GAL、CPLD 等可编程器件的基础上进一步发展的产物,它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

CPLD的结构和工艺与可编程阵列逻辑(Programmable Logic,PAL)一样,而FPGA的结构则类似于门阵列ASIC。简单而言,以乘积项结构方式构成逻辑行为的器件称为CPLD,如Xilinx公司的XC9500系列、Lattice公司的ispLSI系列、Altera的MAX7000S系列等;以查表法结构方式构成逻辑行为的器件称为FPGA,如Altera的FLEXl0K、ACEXlK或Cyclone系列,Xilinx的Spartan系列和Virtex系列等。

总体来讲,CPLD/FPGA 中的逻辑门的数量规模比较大,可以替代几十甚至几千块通用IC(集成电路)芯片。这样的CPLD/FPGA实际上就是一个子系统部件,用户通过编程可以在短时间内把一个通用的CPLD/FPGA芯片配置成用户需要的硬件数字电路。

CPLD/FPGA 是嵌入式硬件工程师在研发过程中常用的两种器件,因为这两种器件既具备ASIC电路高密度和高速度的优点,又具备PLD在短时间内完成功能编制的特点。使用PLD生产的嵌入式系统IC包括嵌入式微处理器、加/解密器、流媒体编/解码器、接口控制器、接口数据转换器、信号发生器、数据采集器等。

2.三防平板方案CPLD和FPGA的结构特点

尽管CPLD、FPGA与其他类型PLD在结构上各有其特点和长处,但它们都是由以下三大部分组成的。

● 可编程二维的逻辑阵列块,它们构成了PLD器件的逻辑核心;

● 可编程的输入/输出块;

● 可编程的连接逻辑块的连线资源,连线资源由各种长度的连线线段组成,其中也有一些可编程的连接开关,它们用于逻辑块之间、逻辑块与输入/输出块之间的连接。

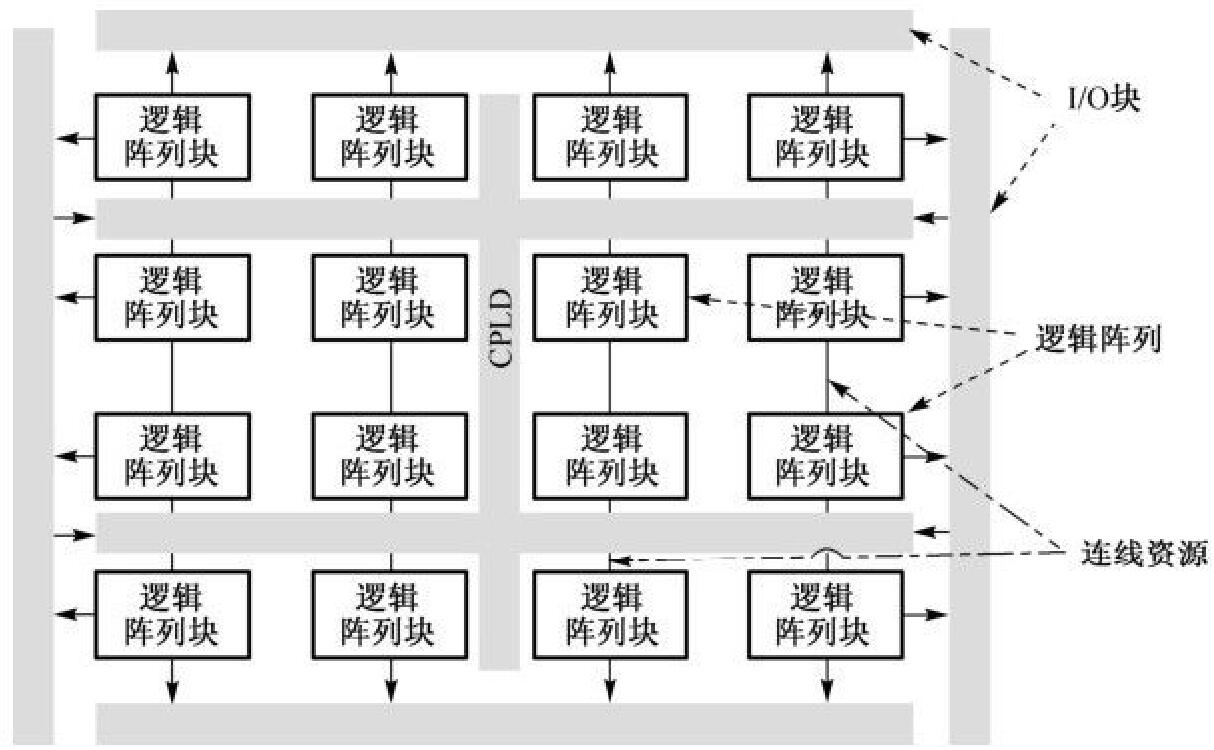

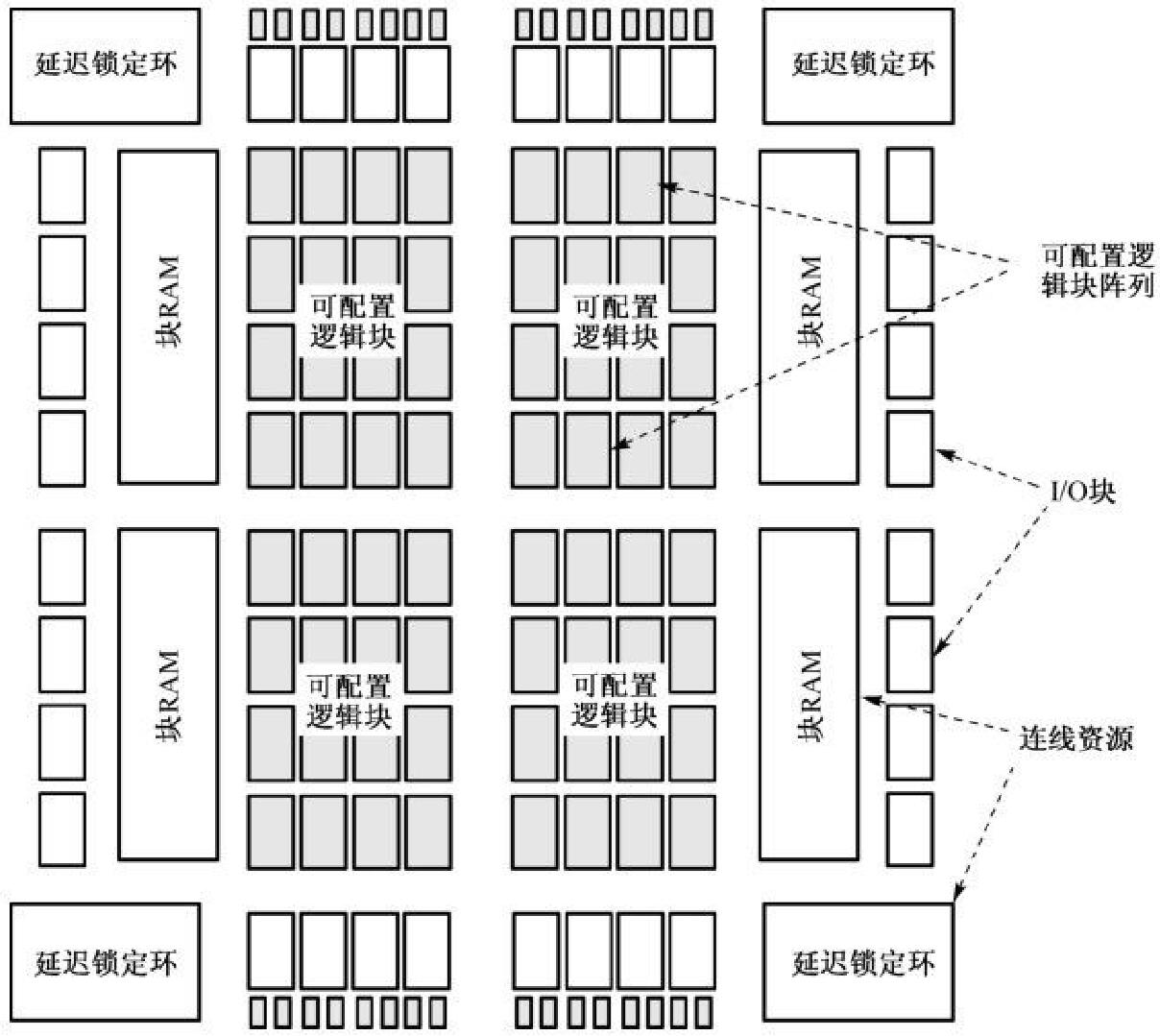

图1和图2分别给出了典型的CPLD和典型的FPGA的结构图,从中可以看到两者结构上的不同,下面简述其中的主要部件功能。

(1)三防平板方案逻辑阵列块(Logic Array Block,LAB):如图7-1所示,每一个LAB都是可编程的,LAB是实现用户逻辑功能的主要单元,由组合逻辑资源和触发器两部分组成。三防平板方案组合逻辑资源通常又称为函数发生器,由于各个系列不同,每个可编程LAB由1~3个功能不尽相同的函数发生器和1~2个触发器组成。

图1 典型CPLD结构图(Altera公司MAX7000系列)

(2)三防平板方案可配置逻辑块(Configurable Logic Block,CLB):如图2所示,每个可配置逻辑模块有4个块,每个块都有4输入查找表(Look Up Table,LUT)、触发器、多路复用器、运算逻辑、载体逻辑以及专门的内部布线,可实现任意的组合电路与时序电路。

(3)延时锁定环(Delay Locked Loop,DLL):主要由一个多种类的延时线和控制逻辑组成,延时线对时钟输入端产生一个延时时钟,分布网线将该时钟分配到器件内的各个寄存器和时钟反馈端。

(4)块RAM(Block RAM):可以配置为双端口RAM或先进先出(FIFO)功能,并提供64位误差校验和纠正(ECC)功能。它能使用户有效地存储数据或者缓冲数据,而无须使用片外存储器。以Virtex-5系列的FPGA为例,每个块RAM的最大容量是36 KB,因此可以配置成2个独立的18 KB块RAM,或者使用一个36 KB块RAM。

目前,三防平板方案中FPGA和CPLD的集成度已经高达500万门/片以上,这样就可以用来开发一些较大规模的数字逻辑电路,特别适合样品研制或小批量产品开发,使产品能够以最快的速度上市。利用FPGA和CPLD进行ASIC设计的优点如下。

● 一个FPGA和CPLD器件可以经过成千上万次的擦除和写入,能够做到反复编程、反复擦除、反复使用,非常适合科研和样机研制;

● 对开发设备和场地无特别要求,只要有一台普通的PC外加一个FPGA和CPLD实验系统就能够开展设计和试验,可以在现场完成功能制定,并满足临时修改要求;

● 投资小,成本低,目标电路的正确性可以在投片之前通过实验系统模拟运行加以验证,避免投片风险;

● 由于PC平台的开发环境普及化,可以同时由多人开发,因此能够缩短设计周期。

3.FPGA和CPLD主要区别

FPGA和CPLD主要区别有如下几个方面。

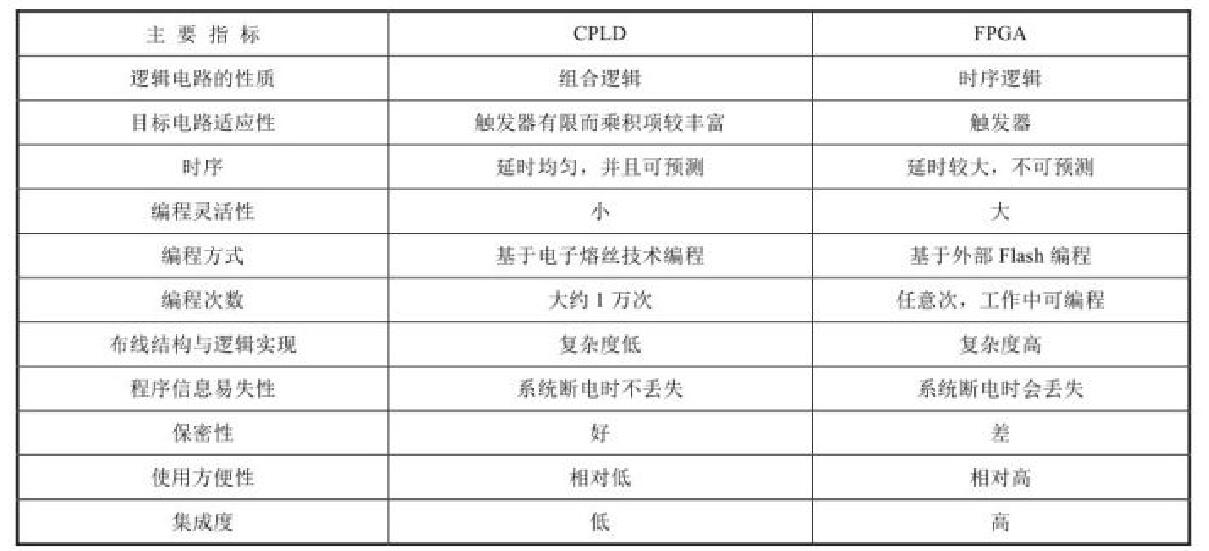

① CPLD更适合完成各种算法和组合逻辑,FPGA更适合完成时序逻辑。也就是说,FPGA更适合触发器丰富的结构,而CPLD更适合触发器有限而乘积项较丰富的结构。

② CPLD的连续式布线结构决定了它的时序延时是均匀的和可以预测的,而FPGA的分段式布线结构决定了其延时的不可预测性。

③ 在编程上,FPGA比CPLD具有更大的灵活性。CPLD通过修改具有内连电路的逻辑功能来编程,FPGA主要通过改变内部连线的布线来编程。FPGA可在逻辑门下编程,而CPLD是在逻辑模块下进行编程的。

④ FPGA的集成度比CPLD高,具有更复杂的布线结构和逻辑实现。

⑤ CPLD比FPGA使用起来更方便。CPLD的编程采用的是基于电子熔丝技术,不需要外部存储器芯片,使用简单;而FPGA的编程信息需存放在Flash等外部存储器上,使用方法复杂。

⑥ CPLD的速度比FPGA快,并且具有较大的时间可预测性。这是由于FPGA是门一级编程,并且逻辑块CLB之间采用分布式互连;而CPLD是逻辑块一级编程,并且其逻辑块之间的互连是集总式的。

⑦ 三防平板方案在编程方式上,CPLD主要是基于E2PROM或Flash存储器编程的,编程次数可达1万次,优点是系统断电时编程信息也不丢失。CPLD 又可分为在编程器上编程和在系统编程两类。FPGA大部分是基于SRAM编程的,编程信息在系统断电时会丢失。每次上电时,需从器件外部将编程数据重新写入SRAM中,其优点是可以任意次编程,可在工作中快速编程,从而实现板级和系统级的动态配置。

⑧ CPLD保密性好,FPGA保密性差。

⑨ 一般情况下,CPLD的功耗要比FPGA大,且集成度越高越明显。

三防平板方案随着复杂可编程逻辑器件(CPLD)密度的提高,数字器件设计人员在进行大型设计时,既灵活又容易,而且产品可以很快进入市场,许多设计人员已经感受到 CPLD容易使用、时序可预测和速度高等优点。然而,在过去由于受到CPLD密度的限制,他们只好转向FPGA和ASIC。现在,设计人员可以体会到密度高达数十万门的CPLD所带来的好处。

CPLD和FPGA这两种可编程逻辑器件之间的主要区别如表1所示。

表1 CPLD和FPGA的区别